# INVESTIGATIONS ON HIGH-FREQUENCY TRANSFORMER ISOLATED CLL RESONANT DC-DC POWER CONVERTER FOR RENEWABLE ENERGY APPLICATIONS

Thesis

Submitted in partial fulfillment of the requirements for the degree of

## **DOCTOR OF PHILOSOPHY**

by

# **UDAY PATIL**

(Registration No.: 158035-EE15F09)

Under the guidance of

### Dr. NAGENDRAPPA H.

Assistant Professor

DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING NATIONAL INSTITUTE OF TECHNOLOGY KARNATAKA SURATHKAL, MANGALORE - 575 025 SEPTEMBER, 2021

#### **DECLARATION**

by the Ph.D. Research Scholar

I hereby *declare* that the Research Thesis entitled "Investigations on High-Frequency Transformer Isolated CLL Resonant DC-DC Power Converter for Renewable Energy Applications" which is being submitted to the National Institute of Technology Karnataka, Surathkal in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy in Department of Electrical and Electronics Engineering is a *bonafide report of the research work carried out by me*. The material contained in this Research Thesis has not been submitted to any University or Institution for the award of any degree.

H.J.

UDAY PATIL (158035-EE15F09) Department of Electrical and Electronics Engineering

Place: NITK-Surathkal Date: 22-09-2021

### **CERTIFICATE**

This is to certify that the Research Thesis entitled "Investigations on High-Frequency Transformer Isolated CLL Resonant DC-DC Power Converter for Renewable Energy Applications" submitted by UDAY PATIL (Register Number, 158035-EE15F09) as the record of the research work carried out by him, is *accepted as the Research Thesis submission* in partial fulfilment of the requirements for the award of degree of **Doctor of Philosophy**.

Dr. Nagendrappa H. (Research Guide)

Gururaj S. Punekar (Chairman-DRPC, EEE Dept.)

#### **ACKNOWLEDGEMENTS**

It gives me immense pleasure and great sense of satisfaction to express my heartfelt gratitude to those who made this dissertation possible.

I would like to express my sincere gratitude to my research supervisor Dr. Nagendrappa H. for his guidance, patience, encouragement and support. He has been a constant source of inspiration throughout this journey. I feel proud to have worked under his guidance.

I wish to thank my research progress assessment committee (RPAC) members Dr. D. N. Gaonkar, Associate Professor, Dept. of Electrical & Electronics Engineering, and Dr. Subhaschandra Kattimani, Associate Professor, Dept. of Mechanical Engineering for their constructive feedback and guidance.

I would like to thank HOD, Dr. Gururaj S Punekar for encouragement and providing valuable suggestions. Also, I would like to thank Dr. Shubhanga K N, Dr. B Venkatesa Perumal and Dr. Vinatha U, former HODs for providing the necessary resources in the department to carry out my research.

I take this opportunity to thank all the teaching and non-teaching staff of EEE Department, NITK, Surathkal.

I thank National Institute of Technology Karnataka (NITK), Surathkal for giving me an opportunity for doing research and Ministry of Human Resource Department (MHRD), Government of India for awarding research scholarship.

I wish to thank all my dear friends for their care, support, valuable inputs and constant encouragement. My stay at NITK, Surathkal was delightful and memorable in the company of my fellow researchers who never let me knew that I am away from home. I am indebted to all of them.

I would like to express my deepest gratitude towards my family for their patience, care and selfless love which drew me with inspiration to carry out my research.

Also, this dissertation is dedicated to my parents, who have been a great source of motivation and inspiration.

Finally, I thank God Almighty for giving me strength at all times.

UDAY PATIL

#### ABSTRACT

Renewable energy sources have been the most promising substitute for conventional energy sources and are employed worldwide due to their cleanliness and sustainability. The power generated by using renewable energy sources is highly fluctuating as it depends on the environmental conditions and other operating conditions. A power conditioning unit comprising of DC-DC converter is required to convert this fluctuating power into a usable constant power. There is an increase in the demand of DC-DC power converters with compact size, higher power density and higher conversion efficiency for the applications involving wide variations in input voltage and load. These converters are also used in applications where electrical isolation is required. The intent of this research is in finding a suitable soft-switching DC-DC power converter topology and investigating on its performance for the applications in renewable energy generation.

In this dissertation, literature review on various resonant power converter topologies and gating control scheme is carried out. The full bridge CLL resonant converter topology and fixed frequency gating scheme are chosen for the study. Three different converter topologies with suitable gating scheme were proposed and examined in detail. The first converter presented is a high-frequency transformer isolated CLL resonant DC-DC power converter operated with phase-shift gating scheme and modified PWM gating scheme. Modeling, analysis, design, simulation and experimental results of the converter are presented. Theoretical and experimental results are compared and performance of the converter when operated with both the gating schemes is analysed.

A high-frequency isolated full bridge zero-voltage-transition (ZVT) CLL resonant DC-DC converter operated with a modified PWM gating scheme has been

proposed. Various modes of operation of the converter are described using typical operating waveforms and equivalent circuit diagrams. Analysis, design, simulation and experimental results are presented and discussed. The proposed converter is able to provide ZVS for all the inverter switches for entire variations in input voltage and loading conditions.

A three-phase interleaved full bridge CLL resonant DC-DC converter with fixed frequency modified PWM gating control has been proposed for medium to high power applications. Modeling and analysis of the converter is presented and the design procedure using a design example is explained. The designed converter is simulated using PSIM software to predict the performance of the converter for variations in input voltage and load conditions. The converter operates in ZVS for all the inverter switches with minimum input voltage and only one switch loses ZVS in each bridge/module for higher input voltages.

# Contents

| List of Figures(ix)                                                       |

|---------------------------------------------------------------------------|

| List of Tables(xvii)                                                      |

| Chapter 1 1                                                               |

| INTRODUCTION 1                                                            |

| 1.1 Introduction1                                                         |

| 1.2 Introduction to Fuel Cells                                            |

| 1.2.1 Voltage and Current Characteristics of Fuel Cell                    |

| 1.2.2 Voltage and Current Characteristics at Different Rate of Fuel Flow5 |

| 1.3 Introduction to Solar Power Generation5                               |

| 1.3.1 Modeling of Photovoltaic Cell6                                      |

| 1.4 DC-DC Power Conversion                                                |

| 1.4.1 Linear Voltage Regulator8                                           |

| 1.4.2 Switched Mode Converters9                                           |

| 1.4.3 Soft-Switching Converters9                                          |

| 1.5 Switching Mechanism10                                                 |

| 1.5.1 Hard-Switching                                                      |

| 1.5.2 Soft-Switching11                                                    |

| 1.5.3 Zero Voltage Switching11                                            |

| 1.5.4 Zero Current Switching13                                            |

| 1.6 Motivation for the Work14                                             |

| 1.7 Objectives                                                            |

| 1.8 Outline of the Dissertation                                           |

| Chapter 2 19                                                              |

| LITERATURE REVIEW ON SOFT-SWITCHING RESONANT                              |

| CONVERTERS 19                                                             |

| 2.1 Resonant Converters                                                   |

| 2.1.1 Series Resonant Converters                                          |

| 2.1.2 Parallel Resonant Converters21                                      |

| 2.1.3 Three Element Resonant Converters22                                 |

| 2.1.3.1 Series-Parallel Resonant Converters (LCC Resonant Converter)                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1.3.2 Modified-Series Resonant Converter (LCL-Type Resonant<br>Converter)23                                                                   |

| 2.1.3.3 CLL Resonant Converter24                                                                                                                |

| 2.1.4 Zero Voltage Transition Resonant Converter25                                                                                              |

| 2.1.5 Parallel Dual Series Resonant Converter26                                                                                                 |

| 2.2 Gating Control Scheme27                                                                                                                     |

| 2.2.1 Variable Frequency Gating Scheme28                                                                                                        |

| 2.2.2 Fixed Frequency Gating Scheme28                                                                                                           |

| 2.3 Selection of Converter Topology and Gating Control Scheme29                                                                                 |

| 2.4 Conclusion                                                                                                                                  |

| Chapter 3                                                                                                                                       |

| HIGH FREQUENCY CLL RESONANT DC-DC CONVERTER OPERATED<br>WITH PHASE-SHIFT AND MODIFIED PWM GATING SCHEME:<br>ANALYSIS, DESIGN AND IMPLEMENTATION |

| 3.1 Introduction                                                                                                                                |

| 3.2 Circuit Configuration and Principle of Operation                                                                                            |

| 3.2.1 Operating Modes with Phase-Shift Gating Scheme                                                                                            |

| 3.2.2 Operating Modes with Modified PWM Gating Scheme                                                                                           |

| 3.3 Modeling and Steady State Analysis of the Converter                                                                                         |

| 3.3.1 Assumptions                                                                                                                               |

| 3.3.2 Modeling of the Converter                                                                                                                 |

| 3.3.3 Steady State Analysis of the Converter                                                                                                    |

| 3.4 Design Considerations                                                                                                                       |

| 3.5 Simulation Results with PGS and MGS                                                                                                         |

| 3.5.1 Steady-State Conditions:                                                                                                                  |

| 3.5.2 Performance under Step Changes in Load:                                                                                                   |

| 3.6 Experimental Results and Discussion                                                                                                         |

| 3.7 Conclusion                                                                                                                                  |

| Chapter 4                                                                                                                                       |

| -                                                                                                                                               |

| ANALYSIS AND DESIGN OF A HIGH-FREQUENCY TRANSFORMER<br>ISOLATED FULL BRIDGE ZVT CLL RESONANT DC-DC CONVERTER71                                  |

| 4.1 Introduction71                                                                                                                              |

|                                                                                                                                                                             | 73                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

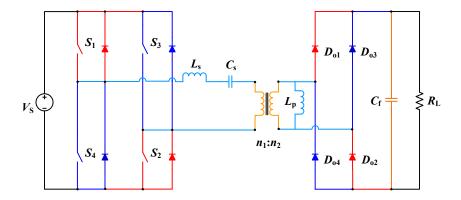

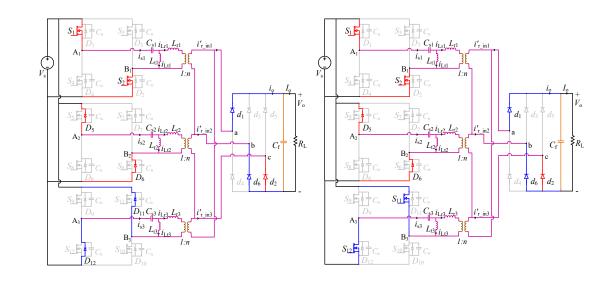

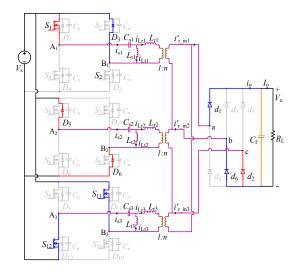

| 4.2.1 Circuit Configuration                                                                                                                                                 | 73                                                                                                       |

| 4.2.2 Modes of Operation                                                                                                                                                    | 75                                                                                                       |

| 4.3 Modeling and Analysis of the Converter                                                                                                                                  | 80                                                                                                       |

| 4.3.1 Converter Modeling                                                                                                                                                    | 80                                                                                                       |

| 4.3.2 Steady State Analysis of the Converter                                                                                                                                | 82                                                                                                       |

| 4.4 Design of the Converter                                                                                                                                                 | 84                                                                                                       |

| 4.4.1 Design Trade-off                                                                                                                                                      | 84                                                                                                       |

| 4.4.2 Design of ZVT Auxiliary Circuit                                                                                                                                       | 87                                                                                                       |

| 4.5 Simulation Results                                                                                                                                                      | 88                                                                                                       |

| 4.6 Experimental Results                                                                                                                                                    | 92                                                                                                       |

| 4.7 Conclusion                                                                                                                                                              | 98                                                                                                       |

| Chapter 5                                                                                                                                                                   | 99                                                                                                       |

| ANALYSIS AND DESIGN OF THREE PHASE INTERLEAVED F                                                                                                                            | ULL                                                                                                      |

| BRIDGE CLL RESONANT CONVERTER OPERATED WITH FL                                                                                                                              | KED                                                                                                      |

| FREQUENCY MODIFIED PWM GATING CONTROL                                                                                                                                       | 99                                                                                                       |

| 5.1 Introduction                                                                                                                                                            | 99                                                                                                       |

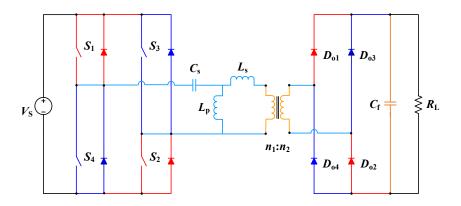

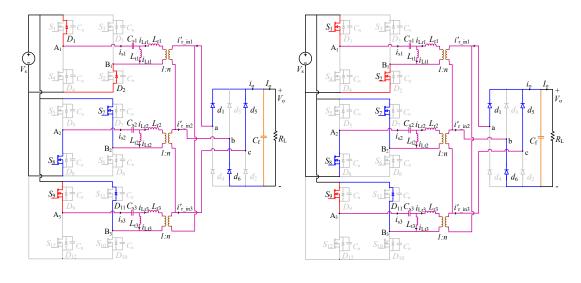

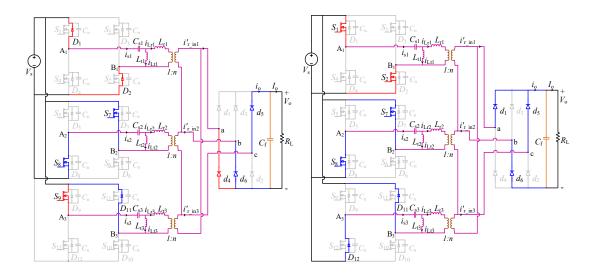

| 5.2 Circuit Configuration and Operation Principle                                                                                                                           | . 102                                                                                                    |

| 5.3 Analysis and Design Procedure                                                                                                                                           |                                                                                                          |

|                                                                                                                                                                             | . 114                                                                                                    |

| 5.3.1 Modeling of the Converter                                                                                                                                             |                                                                                                          |

| <ul><li>5.3.1 Modeling of the Converter</li><li>5.3.2 Converter Analysis</li></ul>                                                                                          | . 115                                                                                                    |

|                                                                                                                                                                             | . 115<br>. 116                                                                                           |

| 5.3.2 Converter Analysis                                                                                                                                                    | . 115<br>. 116<br>. 118                                                                                  |

| <ul><li>5.3.2 Converter Analysis</li><li>5.3.3 Converter Design</li></ul>                                                                                                   | . 115<br>. 116<br>. 118<br>. 120                                                                         |

| <ul> <li>5.3.2 Converter Analysis</li> <li>5.3.3 Converter Design</li> <li>5.4 Simulation Results</li> </ul>                                                                | . 115<br>. 116<br>. 118<br>. 120<br>. 127                                                                |

| <ul> <li>5.3.2 Converter Analysis</li></ul>                                                                                                                                 | . 115<br>. 116<br>. 118<br>. 120<br>. 127<br>. 129                                                       |

| <ul> <li>5.3.2 Converter Analysis.</li> <li>5.3.3 Converter Design.</li> <li>5.4 Simulation Results.</li> <li>5.5 Conclusion</li> <li>Chapter 6</li> </ul>                  | . 115<br>. 116<br>. 118<br>. 120<br>. 127<br>. 129<br>. 129                                              |

| 5.3.2 Converter Analysis<br>5.3.3 Converter Design<br>5.4 Simulation Results<br>5.5 Conclusion<br>Chapter 6<br>CONCLUSIONS AND FUTURE SCOPE                                 | . 115<br>. 116<br>. 118<br>. 120<br>. 127<br>. 129<br>. 129<br>. 129                                     |

| 5.3.2 Converter Analysis<br>5.3.3 Converter Design<br>5.4 Simulation Results<br>5.5 Conclusion<br>Chapter 6<br>CONCLUSIONS AND FUTURE SCOPE<br>6.1 Summary of the Work Done | . 115<br>. 116<br>. 118<br>. 120<br>. 127<br>. 129<br>. 129<br>. 129<br>. 131                            |

| <ul> <li>5.3.2 Converter Analysis</li></ul>                                                                                                                                 | . 115<br>. 116<br>. 118<br>. 120<br>. 127<br>. 129<br>. 129<br>. 129<br>. 131<br>. 132                   |

| <ul> <li>5.3.2 Converter Analysis</li></ul>                                                                                                                                 | . 115<br>. 116<br>. 118<br>. 120<br>. 127<br>. 129<br>. 129<br>. 129<br>. 131<br>. 132                   |

| <ul> <li>5.3.2 Converter Analysis</li></ul>                                                                                                                                 | . 115<br>. 116<br>. 118<br>. 120<br>. 127<br>. 129<br>. 129<br>. 129<br>. 131<br>. 132<br>. 133<br>. 145 |

# List of Figures

| Fig. 1.1:  | Block diagram of power electronic interface of renewable energy sources   |

|------------|---------------------------------------------------------------------------|

|            | with the utility grid/load2                                               |

| Fig. 1.2:  | Block diagram of an isolated resonant DC-DC converter                     |

| Fig. 1.3:  | V-I characteristics of the fuel cell                                      |

| Fig. 1.4:  | V-I characteristics of the fuel cell at different rates of fuel flow      |

| Fig. 1.5:  | I-V characteristics of a typical PV module7                               |

| Fig. 1.6:  | Simplified equivalent circuit of a photovoltaic cell7                     |

| Fig. 1.7:  | Linear voltage regulator                                                  |

| Fig. 1.8:  | Full bridge switched mode converter9                                      |

| Fig. 1.9:  | (a) Typical MOSFET device with snubber. (b) Waveforms of switch voltage   |

|            | $(v_{sw})$ and current $(i_{sw})$ during hard-switching                   |

| Fig. 1.10: | ZVS mechanism (a) Full bridge resonant converter (b) Waveforms of voltage |

|            | across and current through switch $S_1$                                   |

| Fig. 1.11: | ZCS mechanism (a) Full bridge resonant converter (b) Waveforms of voltage |

|            | across and current through switch $S_1$                                   |

| Fig. 2.1:  | Series resonant converter                                                 |

| Fig. 2.2:  | Parallel resonant converter                                               |

| Fig. 2.3:  | Series-parallel resonant converter                                        |

| Fig. 2.4:  | LCL resonant converter                                                    |

| Fig. 2.5:  | CLL resonant converter                                                    |

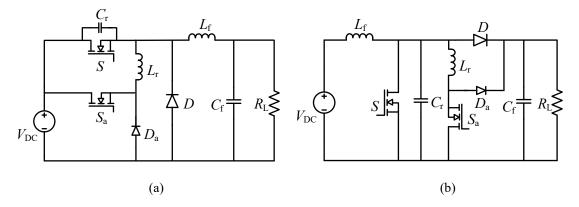

| Fig. 2.6:  | ZVT PWM resonant converters. (a) ZVT buck converter. (b) ZVT boost        |

|            | converter                                                                 |

| Fig. 2.7:  | Fixed frequency parallel dual series resonant converter                   |

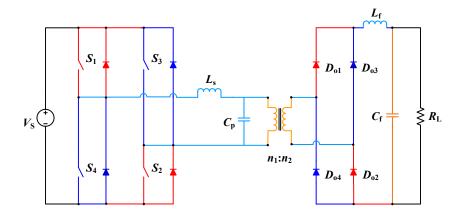

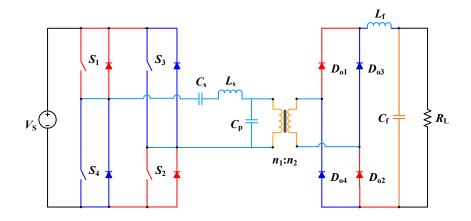

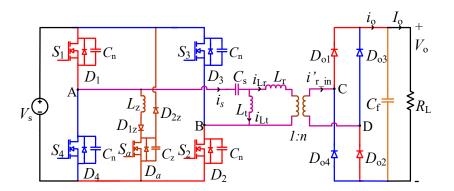

| Fig. 3.1:  | Schematic of high-frequency full bridge CLL resonant DC-DC converter.36   |

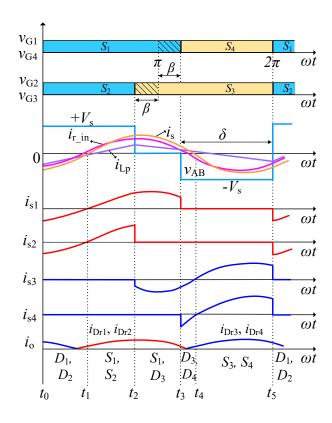

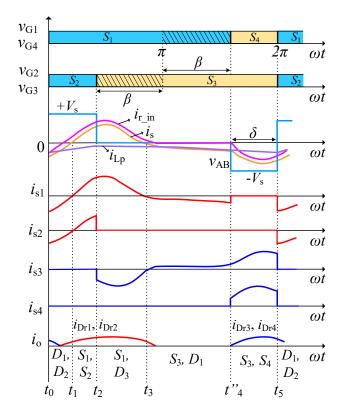

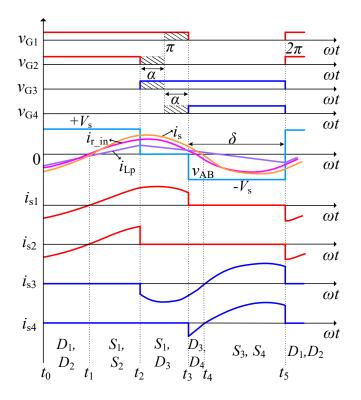

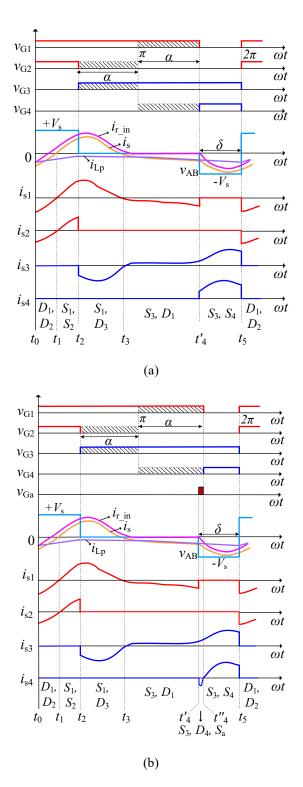

| Fig. 3.2:  | Phase-shift gating scheme and operating waveforms of the converter when   |

|            | applied with minimum input voltage (Mode I)                               |

|            |                                                                           |

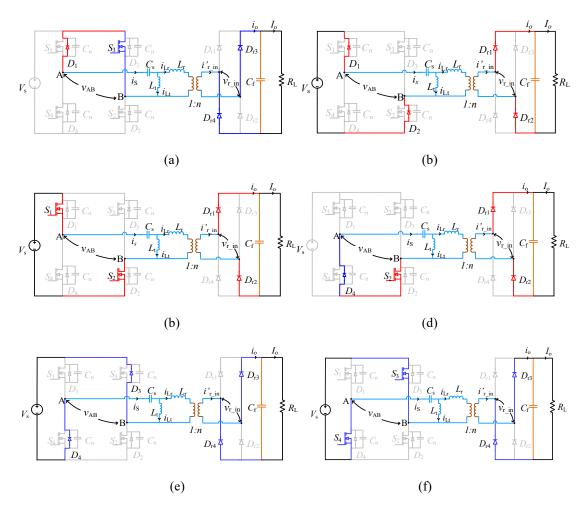

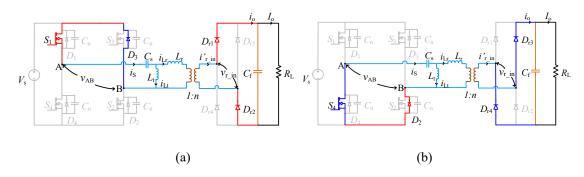

| Fig. 3.3:  | Equivalent circuits for different operating states of Mode-I when operated                     |

|------------|------------------------------------------------------------------------------------------------|

|            | with PGS.(a) State I. (b) State II. (c) State III. (d) State IV. (e) State V. (f) State VI     |

| Fig. 3.4:  | Phase-shift gating scheme and operating waveforms of the converter when                        |

|            | applied with maximum input voltage (Mode II)40                                                 |

| Fig. 3.5:  | Equivalent circuits for different operating states of Mode-II when operated                    |

|            | with PGS. (a) State II'. (b) State V'41                                                        |

| Fig. 3.6:  | Modified PWM gating scheme and operating waveforms of the converter                            |

|            | when applied with minimum input voltage (Mode I)42                                             |

| Fig. 3.7:  | Equivalent circuits for different operating states of Mode I when operated                     |

|            | with MGS. (a) State I. (b) State II. (c) State III. (d) State IV. (e) State V43                |

| Fig. 3.8:  | Modified PWM gating scheme and operating waveforms of the converter                            |

|            | when applied with maximum input voltage (Mode II)44                                            |

| Fig. 3.9:  | Equivalent circuits for different operating states of Mode II when operated                    |

|            | with MGS. (a-b) State IV"45                                                                    |

| Fig. 3.10: | : (a) Transformer equivalent circuit of the converter. (b) Incorporating the                   |

|            | $\Delta$ -Y transformed parameters in the circuit. (c) Simplified circuit of the               |

|            | converter. (d) Equivalent phasor circuit of the converter47                                    |

| Fig. 3.11: | : Current and voltage waveforms at the input terminals of the rectifier and                    |

|            | current waveform at the output terminal of the rectifier                                       |

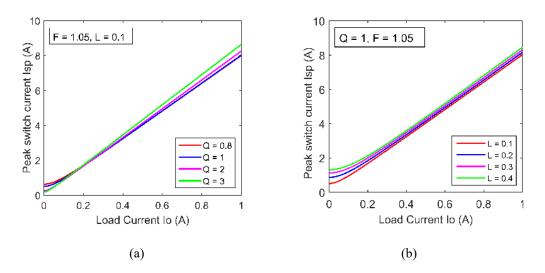

| Fig. 3.12: | : Variations of peak switch current $I_{sp}$ with the output load current $I_{o}$ . (a) For    |

|            | F = 1.05, $L = 0.1$ and for various values of $Q$ . (b) For $Q = 1$ , $F = 1.05$ and           |

|            | for various values of <i>L</i>                                                                 |

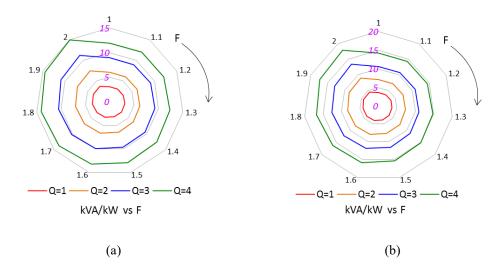

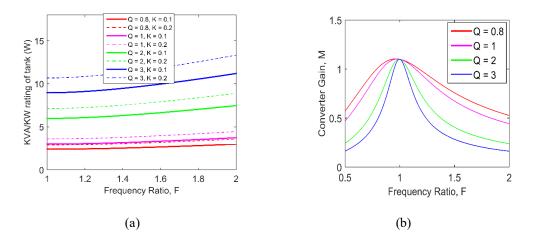

| Fig. 3.13: | : $kVA/kW$ rating of tank network for variations in F from 1 to 2 for different                |

|            | values of $Q$ . (a) For $L = 0.1$ . (b) For $L = 0.2$                                          |

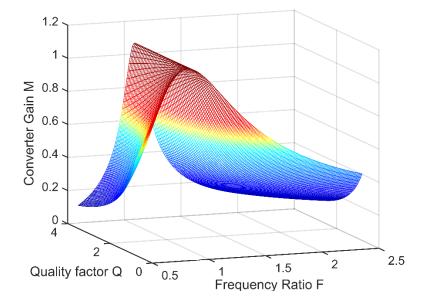

| Fig. 3.14: | : Plot of converter gain $(M)$ with variations in $Q$ and $F$                                  |

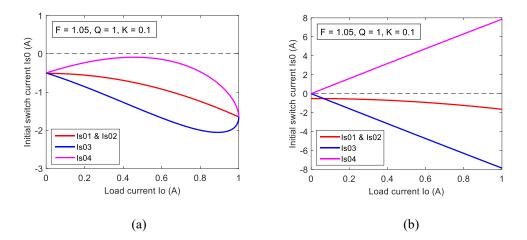

| Fig. 3.15: | : Variations in initial switch current of switches $S_1$ , $S_2$ , $S_3$ and $S_4$ for changes |

|            | in load current $I_0$ with MGS. (a) For $V_{s(min)} = 40$ V. (b) For $V_{s(max)} = 80$ V.55    |

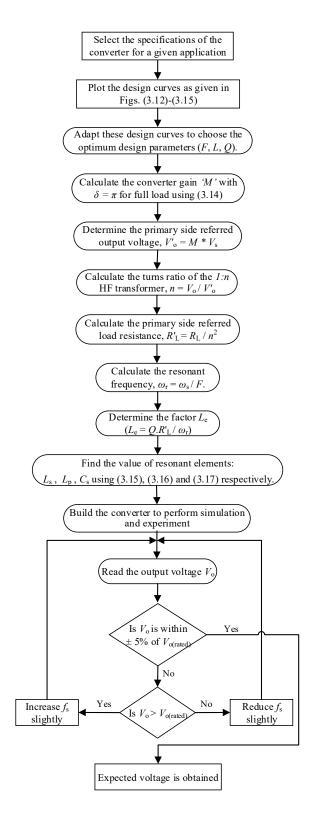

| Fig. 3.16: | : Flowchart for the design procedure of the converter for full-load ( $\delta = \pi$ ) with    |

|            | minimum input voltage applied                                                                  |

|            |                                                                                                |

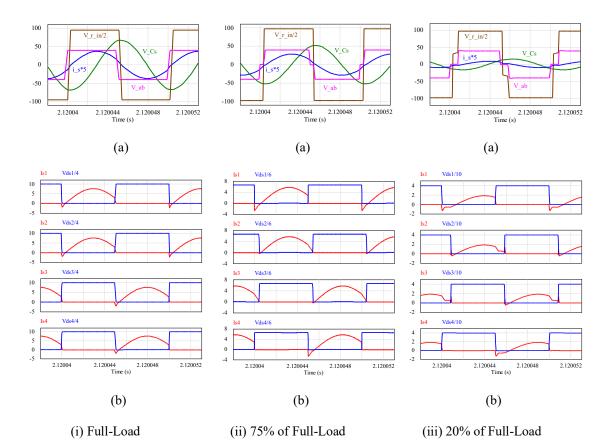

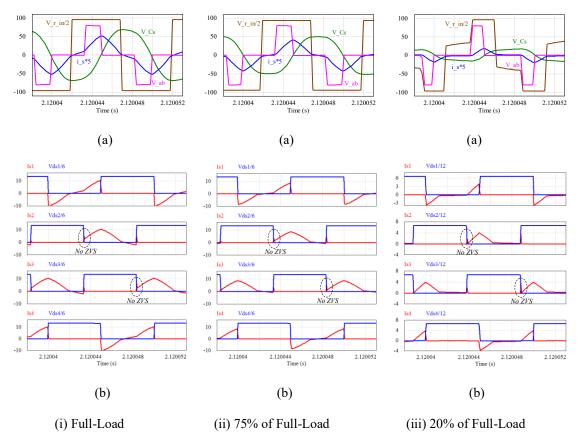

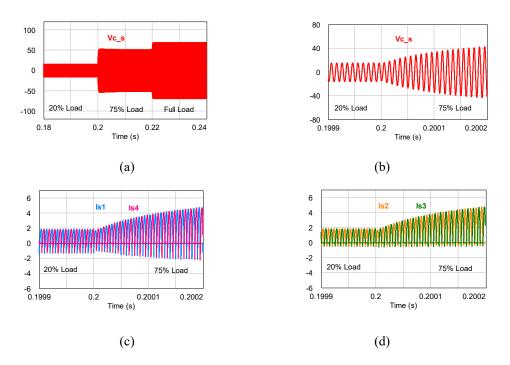

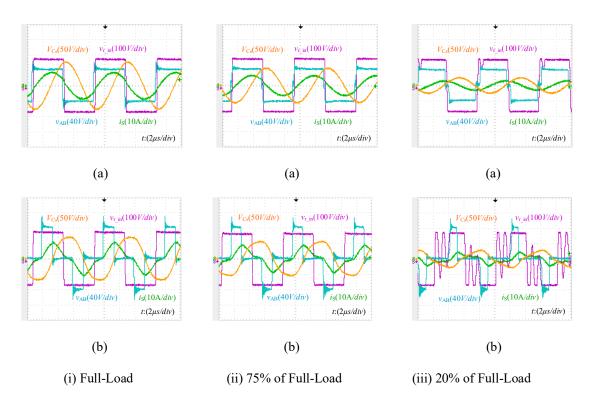

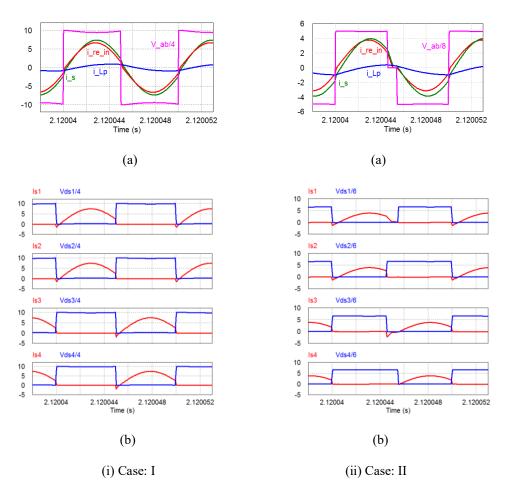

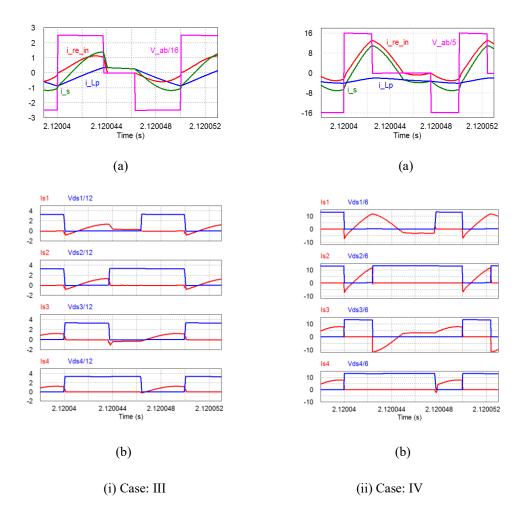

- Fig. 3.18: PSIM simulation results for minimum input voltage V<sub>s(min)</sub> = 40 V when operated with phase-shift gating scheme for: (i) full-load (ii) 75% of full-load and (iii) 20% of full-load, where, (a) resonant current i<sub>s</sub>, inverter output voltage v<sub>AB</sub>, rectifier input voltage v<sub>r\_in</sub>, resonant capacitor voltage v<sub>Cs</sub>.

(b) voltage across (v<sub>ds</sub>) and respective current through (i<sub>s</sub>) switches S<sub>1</sub> S<sub>4</sub>

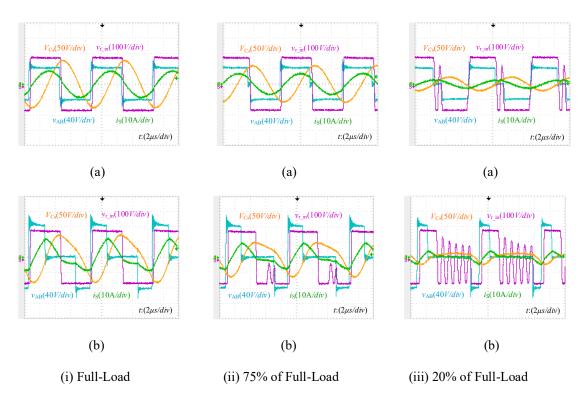

- Fig. 3.19: PSIM simulation results for minimum input voltage V<sub>s(min)</sub> = 40 V when operated with modified PWM gating scheme for: (i) full-load, (ii) 75% of full-load and (iii) 20% of full-load, where, (a) resonant current i<sub>s</sub>, inverter output voltage v<sub>AB</sub>, rectifier input voltage v<sub>r\_in</sub>, resonant capacitor voltage v<sub>Cs</sub>.

(b) voltage across (v<sub>ds</sub>) and respective current through (i<sub>s</sub>) switches S<sub>1</sub> S<sub>4</sub>.

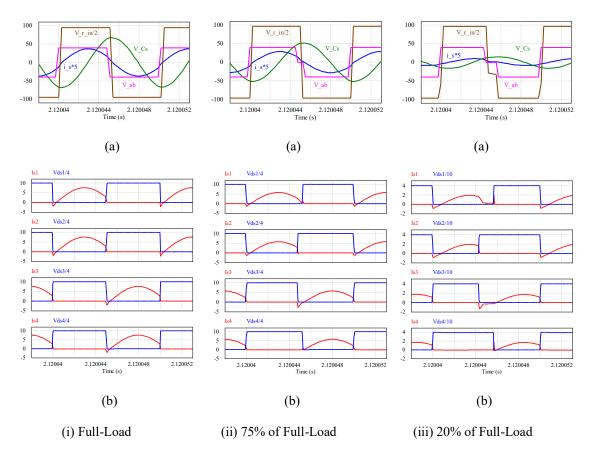

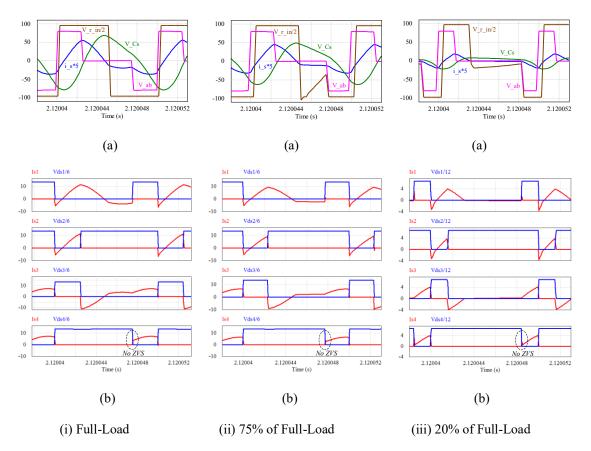

- Fig. 3.21: PSIM simulation results maximum input voltage V<sub>s(max)</sub> = 80 V when operated with modified PWM gating scheme for: (i) full-load, (iii) 75% of full-load and (ii) 20% of full-load, where, (a) resonant current i<sub>s</sub>, inverter output voltage v<sub>AB</sub>, rectifier input voltage v<sub>r\_in</sub>, resonant capacitor voltage v<sub>Cs</sub>.

(b) voltage across (v<sub>ds</sub>) and respective current through (i<sub>s</sub>) switches S<sub>1</sub> S<sub>4</sub>.

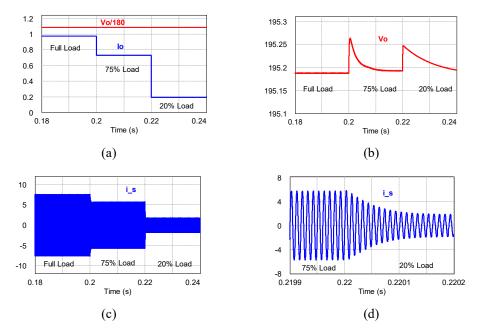

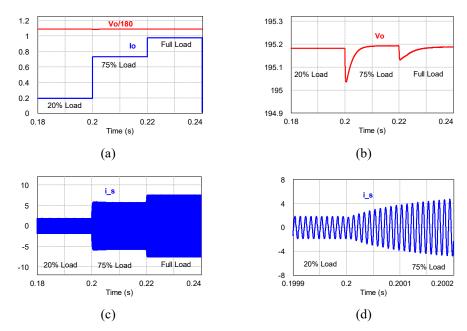

- Fig. 3.22: PSIM simulation results for minimum input voltage  $V_{s(min)} = 40$  V when operated with phase-shift gating scheme for step changes in  $I_0$  from full-load

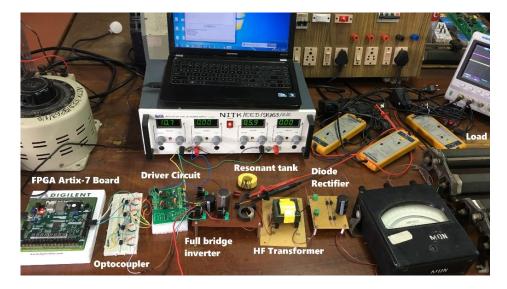

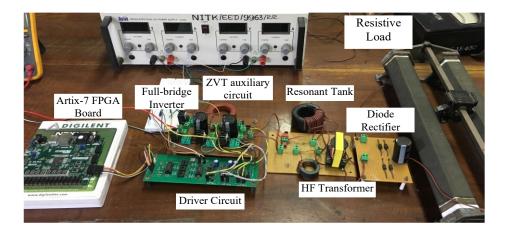

- Fig. 3.27: Photograph of experimental setup of high-freqency transfomer isolated full bridge CLL resonant DC-DC converter with capacitive output filter........68

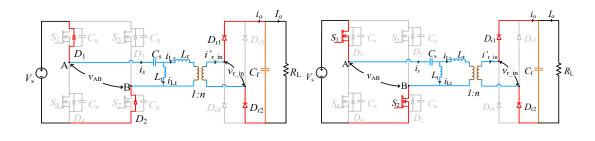

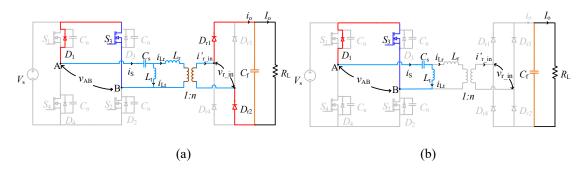

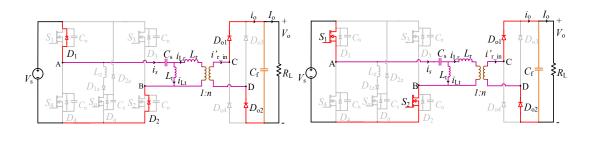

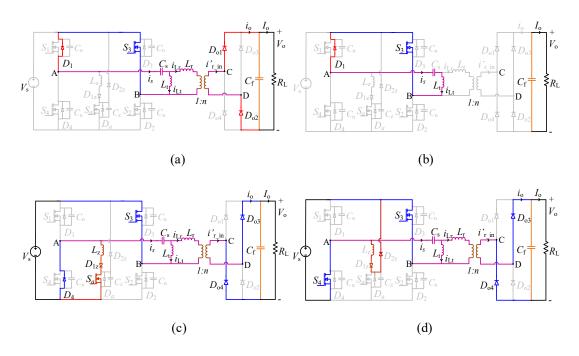

| Fig. 4.3: Equivalent circuit diagrams of the converter for different stages in CCM                   |

|------------------------------------------------------------------------------------------------------|

| (a) Stage I, (b) Stage II, (c) Stage III, (d) Stage IV, (e) Stage V7                                 |

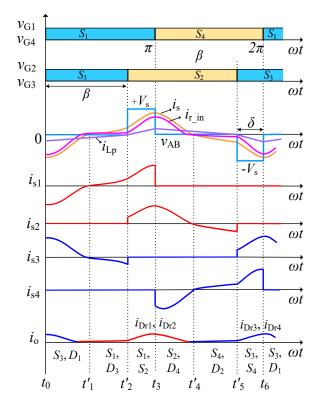

| Fig. 4.4: Typical operating waveform and gating scheme to describe the operation of                  |

| the converter in DCM applied with a maximum input voltage. (a) without                               |

| activation of ZVT (b) with activation of ZV7                                                         |

| Fig. 4.5: Equivalent circuit diagrams of the converter for different stages in DCM                   |

| (a-b) Stage IV', (c-d) Stage IV''                                                                    |

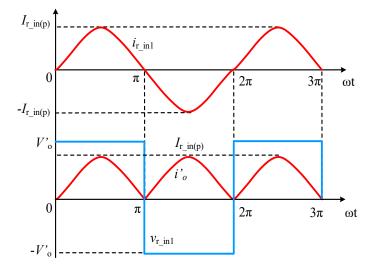

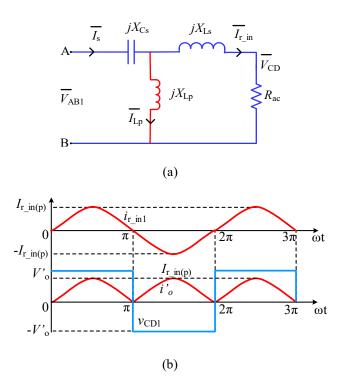

| Fig. 4.6: (a) Simplified circuit of the converter. (b) Waveforms of input current $(i_{r_i})$        |

| and voltage $(v_{CD})$ to the rectifier of the converter                                             |

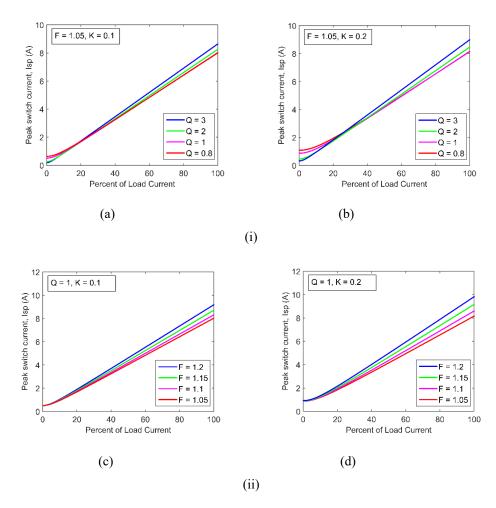

| Fig. 4.7: Peak switch current variation with percentage of full-load current at constant             |

| output voltage for full-load value. (i) For $F = 1.05$ and for different values of                   |

| $Q_{\rm F.}$ (a) $K = 0.1$ (b) $K = 0.2$ . (ii) For $Q_{\rm F} = 1$ and different values of F. (c) K |

| 0.1 (d) $K = 0.2$                                                                                    |

| Fig. 4.8: (a) kVA/kW rating variation of tank circuit versus $F$ for various values of $g$           |

| and for $K = 0.1$ and $K = 0.2$ . (b) Converter gain versus F with variation in $\zeta$              |

|                                                                                                      |

| Fig. 4.9: Simulation waveforms. (a) inverter output voltage $v_{AB}$ , resonant current $v_{AB}$     |

| current through parallel inductor $i_{Lp}$ , current at the input terminals of rectified             |

| $i_{\rm re_in}$ . (b) voltage across switches ( $v_{\rm ds}$ ) and respective current through the    |

| switches ( <i>i</i> <sub>s</sub> )                                                                   |

| Fig. 4.10: Simulation waveforms. (a) inverter output voltage $v_{AB}$ , resonant current $v_{AB}$    |

| current through parallel inductor $i_{Lp}$ , current at the input terminals of rectified             |

| $i_{\rm re_in}$ . (b) voltage across switches ( $v_{\rm ds}$ ) and respective current through the    |

| switches ( <i>i</i> <sub>s</sub> )                                                                   |

| Fig. 4.11: Simulation waveforms. (a) inverter output voltage $v_{AB}$ , resonant current $v_{AB}$    |

| current through parallel inductor $i_{Lp}$ , current at the input terminals of rectified             |

| $i_{\rm re_in}$ . (b) voltage across switches ( $v_{\rm ds}$ ) and respective current through the    |

| switches ( <i>i</i> <sub>s</sub> )                                                                   |

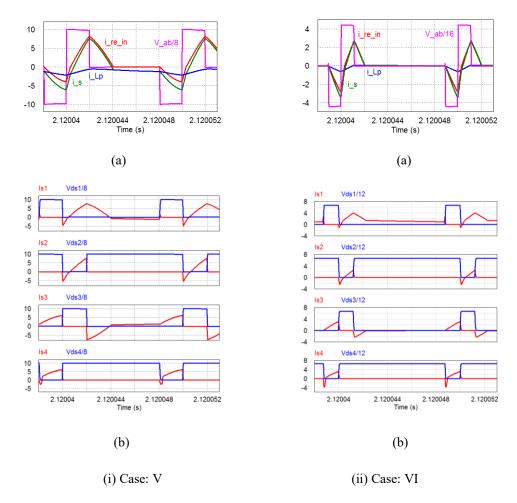

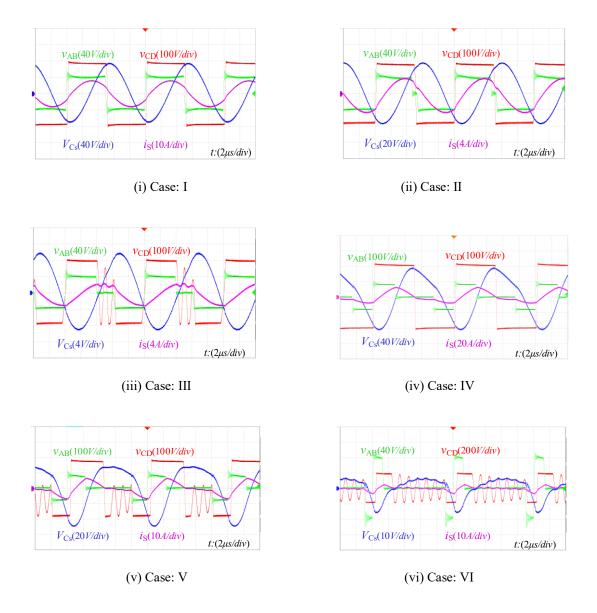

| Fig. 4.12: Experimental results (Cases (I-VI)). Inverte         | r output voltage (v <sub>AB)</sub> , resonant                           |

|-----------------------------------------------------------------|-------------------------------------------------------------------------|

| current $(i_s)$ , voltage across series capacit                 | or $(v_{Cs})$ , voltage across input                                    |

| terminals of rectifier (v <sub>CD</sub> )                       | 94                                                                      |

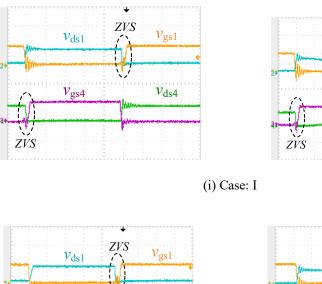

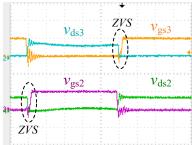

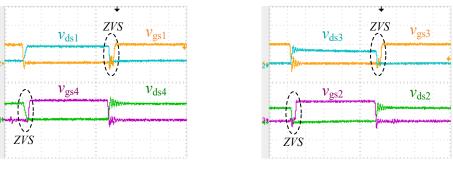

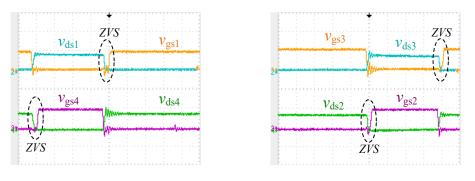

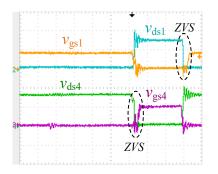

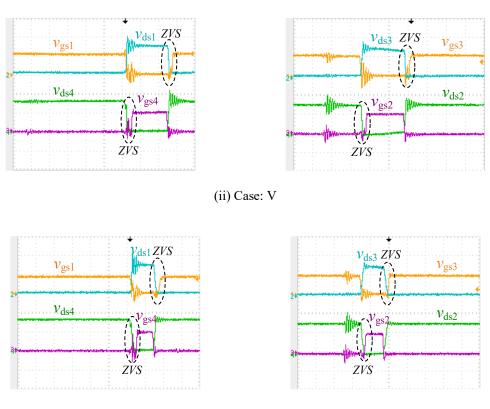

| Fig. 4.13: Experimental results (Cases (I-III)). Voltage        | e across switches ( $v_{ds}$ , 50 V/div)                                |

| and respective gating signal to the switches                    | (v <sub>gs</sub> , 10 V/div)95                                          |

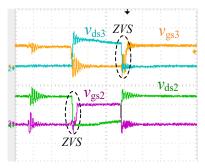

| Fig. 4.14: Experimental results (Cases (IV-VI)). Voltage        | ge across switches ( $v_{ds}$ , 50 V/div)                               |

| and respective gating signal to the switches                    | (v <sub>gs</sub> , 10 V/div)96                                          |

| Fig. 4.15: Photograph of experimental setup of full brid        | dge ZVT CLL resonant DC-DC                                              |

| converter                                                       |                                                                         |

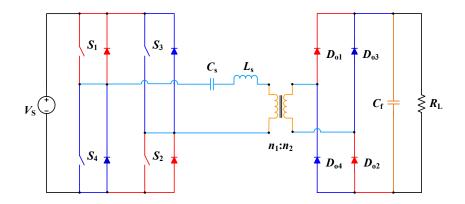

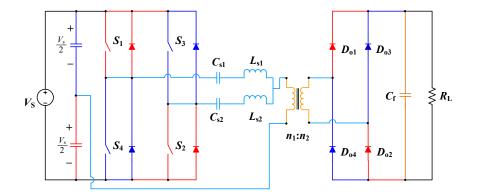

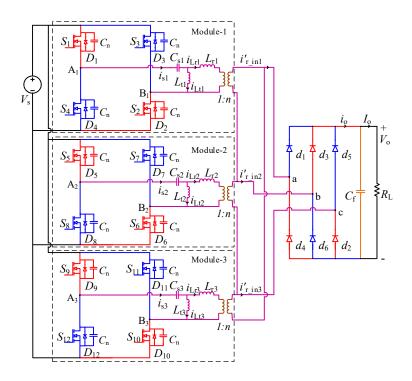

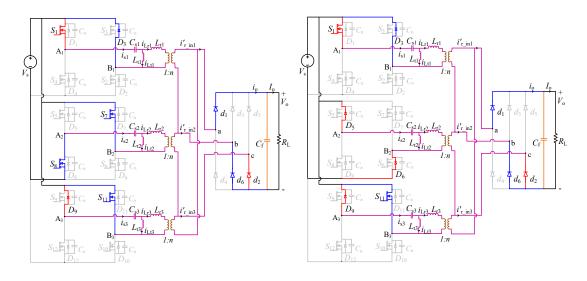

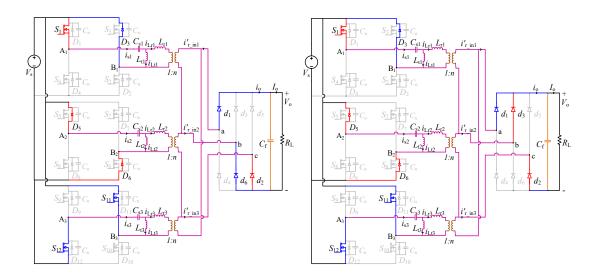

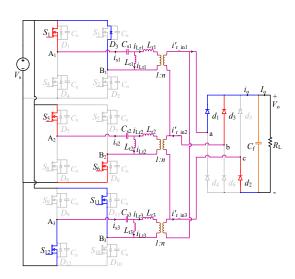

| Fig. 5.1: Three-phase interleaved full-bridge CLL res           | onant DC-DC converter 102                                               |

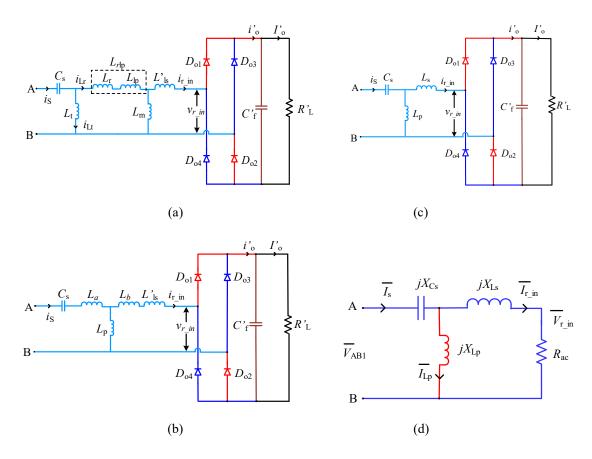

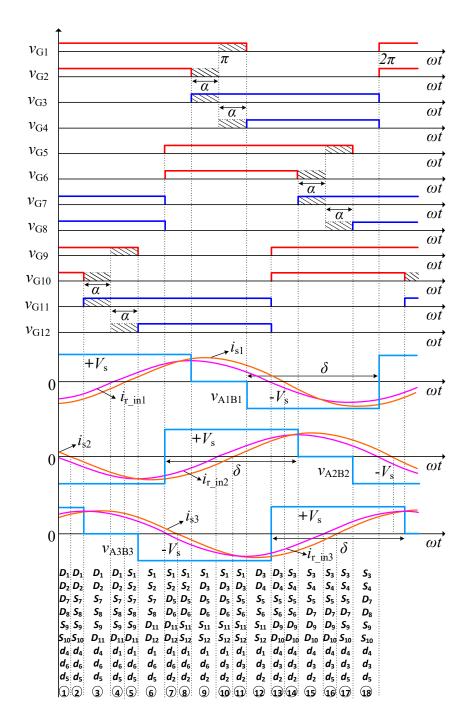

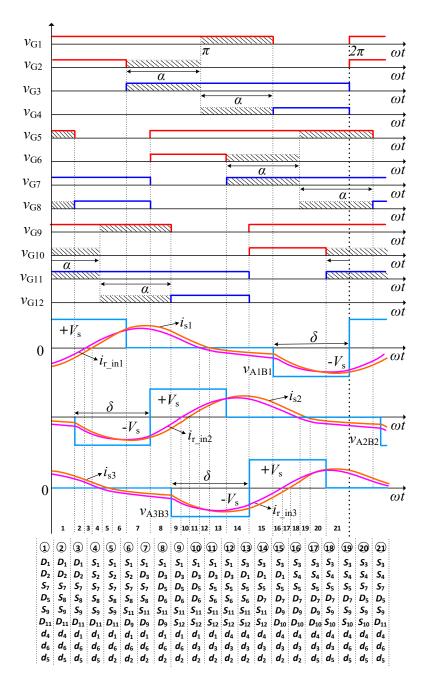

| Fig. 5.2: The key operating waveforms along with the            | e modified PWM gating scheme                                            |

| of Mode-I operation                                             |                                                                         |

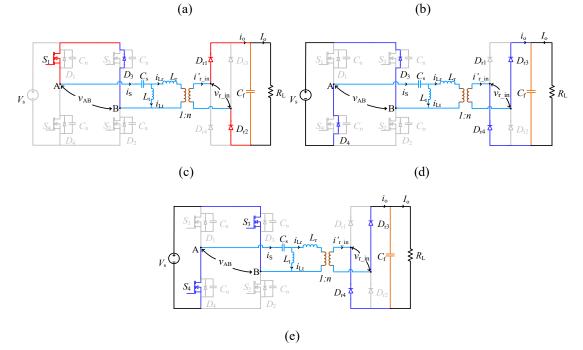

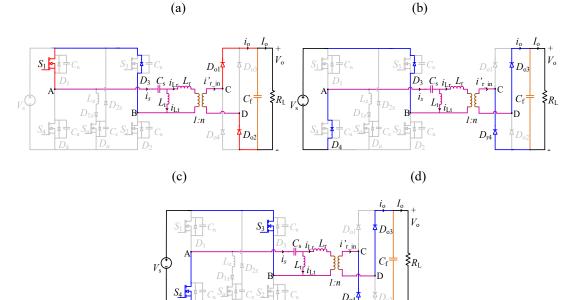

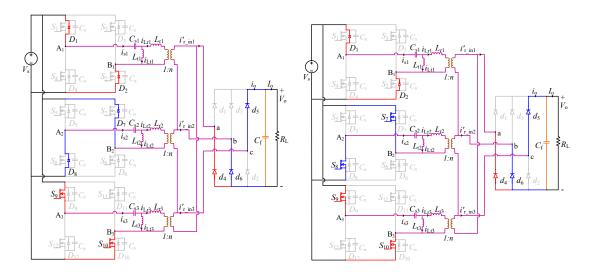

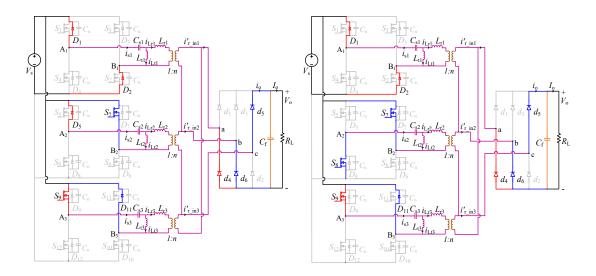

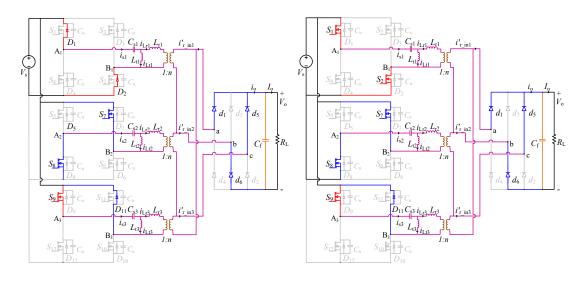

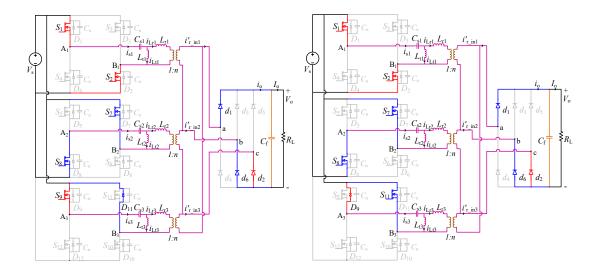

| Fig. 5.3: Equivalent circuit for different operating star       | tes of Mode I operation108                                              |

| Fig. 5.4: The key operating waveforms along with the            | e modified PWM gating scheme                                            |

| of Mode-II operation                                            |                                                                         |

| Fig. 5.5: Equivalent circuit for different operating star       | tes of Mode II operation 113                                            |

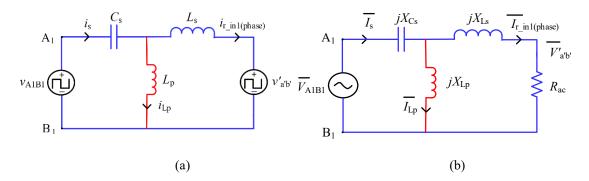

| Fig. 5.6: Phasor equivalent circuit (a) Per phase equ           | vivalent circuit referring all the                                      |

| parameters to primary side of HF transform                      | er. (b) Phasor equivalent circuit                                       |

| of the converter for one of the three-phases of                 | of the converter115                                                     |

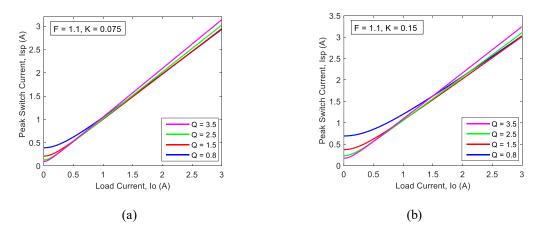

| Fig. 5.7: Peak switch current versus load current               | at constant output voltage for                                          |

| F = 1.1. (a) $K = 0.075$ for different values                   | of $Q$ . (b) $K = 0.15$ for different                                   |

| values of <i>Q</i>                                              |                                                                         |

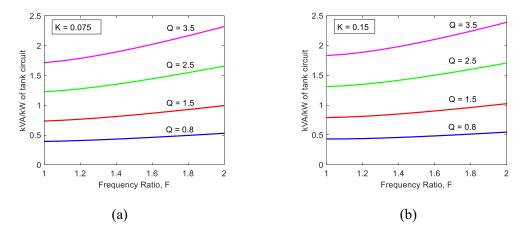

| Fig. 5.8: kVA/kW rating of tank circuit versus frequ            | ency ratio. For $F = 1.1$ and for                                       |

| different values of $Q$ . (a) $K = 0.075$ (b) $K = 0.075$       | 0.15                                                                    |

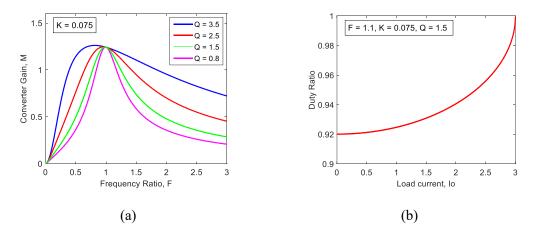

| Fig. 5.9: (a) Converter gain versus frequency ratio. (b         | ) Duty ratio versus load current                                        |

|                                                                 |                                                                         |

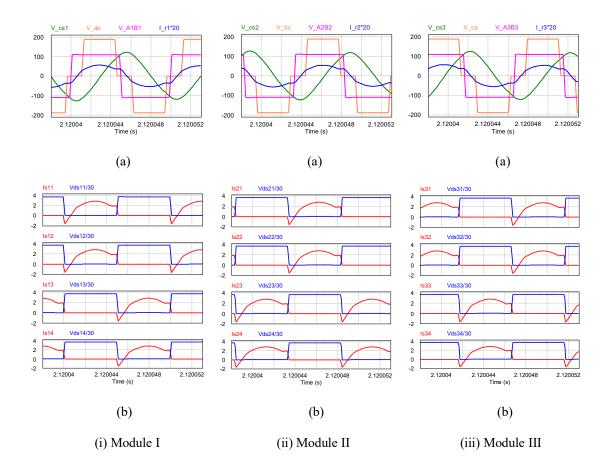

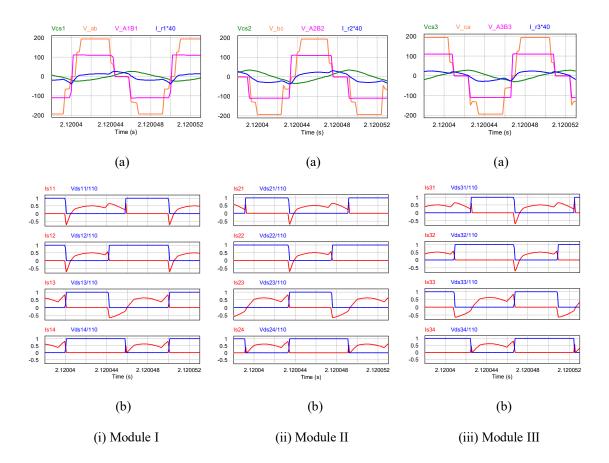

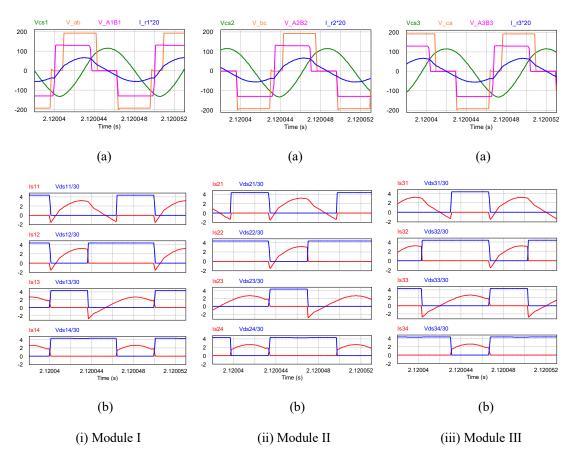

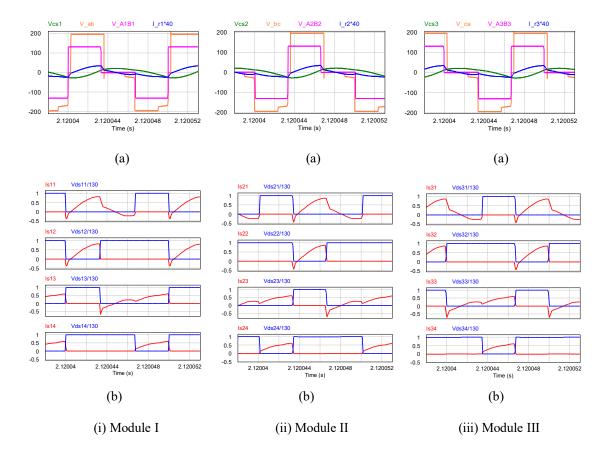

| Fig. 5.10: PSIM simulation results for minimum input            | voltage $V_{s(min)} = 110$ V for full-                                  |

| load condition, where, (a) resonant induct                      | or currents $i_{r1}$ , $i_{r2}$ , $i_{r3}$ ; inverter                   |

| output voltages vA1B1, vA2B2, vA3B3; rectifi                    | er input voltages v <sub>ab</sub> , v <sub>bc</sub> , v <sub>ca</sub> ; |

| resonant capacitor voltages $v_{Cs1}$ , $v_{Cs2}$ , $v_{Cs3}$ . | (b) voltage across the switches                                         |

## List of Tables

| <b>Table 3.1:</b> | Converter specifications and component values                    | 55    |

|-------------------|------------------------------------------------------------------|-------|

| <b>Table 3.2:</b> | Comparison of results when the converter is operated with phase- | shift |

|                   | gating scheme and modified PWM gating scheme                     | 67    |

| Table 4.1:        | Specifications of the converter                                  | 91    |

| <b>Table 4.2:</b> | Comparison of results                                            | 97    |

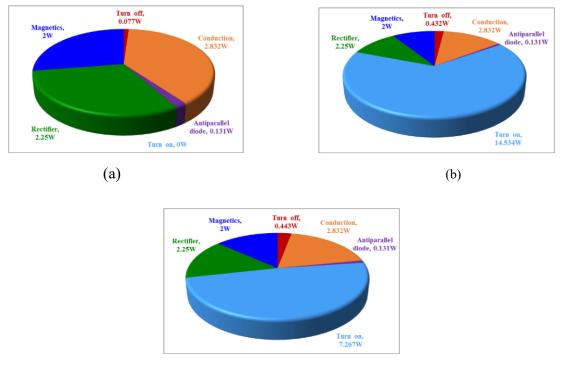

| Table 4.3:        | Power loss breakdown of the converter                            | 97    |

| Table 5.1:        | Specifications of the converter                                  | 120   |

| <b>Table 5.2:</b> | Power loss breakdown of the converter                            | 122   |

| Table 5.3:        | Comparison of results                                            | 127   |

|                   |                                                                  |       |

### **Chapter 1**

### **INTRODUCTION**

The dissertation presents investigations on high-frequency transformer isolated full bridge CLL resonant DC-DC power converter topologies for renewable energy applications. The research findings described in this dissertation contribute to select a suitable, compact and efficient DC-DC soft-switching converter topology that can be used as a power electronic interface between the utility grid/load and renewable energy sources (e.g., fuel cells and solar energy). Detailed modeling, analysis and design is done for the proposed converter topologies. PSIM simulation is carried out and the experimental prototype is built in the laboratory to substantiate theoretical performance predictions.

The introduction of the chapter is given in Section 1.1. The general characteristics and properties of renewable energy sources such as fuel cells and solar energy are described in Section 1.2 and Section 1.3 of this chapter respectively. Section 1.4 explains DC-DC power conversion. The switching mechanism of the DC-DC converter and the soft-switching techniques are given in Section 1.5. The motivation and objectives of this dissertation are discussed in Sections 1.6 and 1.7, respectively. The outline of the dissertation is given in Section 1.8.

#### **1.1 Introduction**

Increase in energy consumption due to the rapid growth in population and industrial expansion has significantly given rise to the environmental issues that must be confronted. There is a huge dependence on many conventional energy sources that are depleting in nature. Power generation using these energy sources leads to increased greenhouse gas emissions and is hazardous to the environment by creating air pollution. Besides the antagonistic issue of global warming, there is a necessity for a reduction in the burning of fossil fuels to accomplish sufficient air quality. The development of an efficient and environmentally friendly power generation is becoming increasingly significant in today's era. Renewable energy sources are the most attractive substitute for conventional (non-renewable) energy sources which have an adverse consequence on the environment and are exhaustible. Renewable energy sources such as wind, solar, hydro and energy conversion technologies such as fuel cells are potential energy sources for providing efficient, clean and eco-friendly electrical power. Power generation using fuel cells has an additional benefit of providing continuous power in all seasons as long as the fuel continuity is sustained. Wind and solar power are intermittent, as these energy sources are much dependent on climatic conditions. The power electronic interface of the renewable energy sources with the utility grid/load is shown in Fig. 1.1.

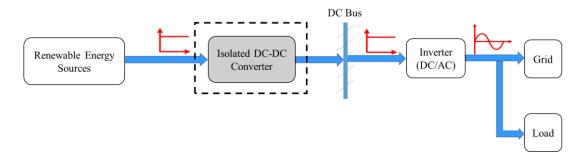

Fig. 1.1: Block diagram of power electronic interface of renewable energy sources with the utility grid/load.

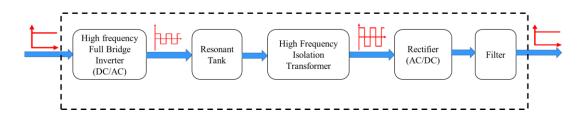

The power generated using renewable energy sources is highly fluctuating due to its dependence on environmental conditions. To convert this varying power into a usable constant power, a power conditioning unit is required. DC-DC converters are one of the important component of this power conditioning unit. The pulse width modulated (PWM) DC-DC converters used for regulating the output voltage suffer from switching losses due to hard-switching. These switching losses increase significantly with high switching frequency resulting in low efficiency. To overcome this drawback, several resonant DC-DC converter topologies have been proposed in the literature (Arazi et al. 2018; Bhat 1995a, 1997b; Bonde and Tamhane 2018; Ching-Jung Tseng and Chern-Lin Chen 1998; Cho et al. 1994; Chuang et al. 2011a, 2012, 2014; Gautam and Bhat 2013; Johnson and Erickson 1988; Kazimierczuk and Wang 1992; Krishnaswami and Mohan 2009; Lin et al. 2017; Morrison 1992; Oruganti and How 1993; Steigerwald 1988; Wang et al. 2005; Wu et al. 2017a, 2008). The resonant DC-DC converter as shown in Fig.1.2, can withstand the variation in input voltage and load while providing soft-switching features. High-frequency switched full bridge resonant DC-DC converters are extensively used for power applications that have an advantage of reduced size of magnetics and filters.

Fig. 1.2: Block diagram of an isolated resonant DC-DC converter.

#### **1.2 Introduction to Fuel Cells**

Fuel cells are electrochemical devices that convert chemical energy of a fuel directly into electrical energy and heat by oxidizing hydrogen, resulting in power generation with high efficiency and low environmental impacts. Fuel cells can produce electricity continuously for as long as fuel and oxygen are supplied.

#### 1.2.1 Voltage and Current Characteristics of Fuel Cell

The actual cell potential is decreased from its ideal potential because of several types of irreversible losses such as activation-related losses, ohmic losses, mass transport-related losses. These losses are often referred to as polarization or overvoltage. Of these polarizations, only the ohmic losses actually behave as

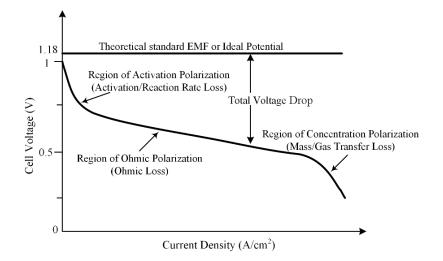

resistance. The V-I diagram (Edition and Virginia 2004; Monti et al. 2002; Rathore 2008) generally for low temperature fuel cells with the effects of the three loss categories are illustrated in Fig. 1.3. In the region of activation polarization for a very small increase in current the voltage drops rapidly. These losses depend on the electrocatalyst material and microstructure, chemical reactions and partially on the current density. Voltage decreases linearly with increasing current in the region of ohmic polarization. This region is the normal operating region of fuel cells. Ohmic losses are caused by ionic resistance in the electrodes and electrolyte, electronic resistance in current collectors, electrodes, interconnects and contact resistances. In the region of transportation polarization, voltage starts to collapse rapidly when current exceeds a certain critical value. These losses depend strongly on the reactant activity, electrode and current density. This critical point of the V-I characteristic represents the maximum limit of safe operation for the cell. With the significant losses, the fuel cell may get damaged for a long duration of operation in this region.

Fig. 1.3: V-I characteristics of the fuel cell.

#### 1.2.2 Voltage and Current Characteristics at Different Rate of Fuel Flow

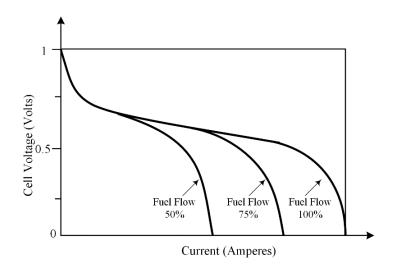

The fuel cells produce electrical power which is variable as it depends on the pressure of hydrogen and oxygen gases. Fig. 1.4 depicts the voltage-current characteristics of the fuel cell at different rate of fuel flow taken into account (Krein et al. 2004; Rathore 2008). The flow of fuel should be adjusted to give the absolute match for a given electrical load. This causes two problems. The flow rate of fuel cannot be adjusted quickly as the load because the internal chemistry (stoichiometry) must reach equilibrium well before the cell can support change in load. If the electrical load increases too quickly, it could drive the curve over the critical point exceeding maximum power transfer and overheating of the fuel cell stack with extra losses. The dynamics of fuel flow and diffusion of reactants are such that the time constant ranges from several seconds to several minutes for different fuel cell technologies.

Fig. 1.4: V-I characteristics of the fuel cell at different rates of fuel flow.

#### **1.3 Introduction to Solar Power Generation**

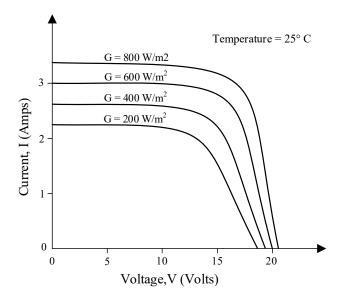

Solar energy is one of the most attractive means of renewable power generation. Sizing of the power supply grid plays a significant role in supplying electricity in a distant region at a fair price. Therefore, photovoltaic (PV) systems are an excellent option for low to medium power levels in remote areas due to the simple scaling of the input power source (Enslin 1990; Singh 2013). The energy conversion efficiency primarily depends on the power-generating PV panels. It is the outcome of numerous efficiencies of the cascaded device, as the energy is transmitted from the sun via the PV system, the regulators, the battery, cabling and an inverter to supply the ac load (Piegari and Rizzo 2010). Weather conditions also influence efficiency, which depends non-linearly on the irradiation level and temperature. The I-V characteristics of a typical PV module for different irradiances (G) at a temperature of 25° C is shown in Fig. 1.5. The PV system power output is proportional to the insolation levels determined in every angular location on the surface of the solar cell. Since solar energy often depends on temperature and panel voltage, maximum power from the solar array needs to be obtained. Various strategies for maximizing output power were suggested and developed (Ali et al. 2020; Bazzi and Krein 2011; Poulek and Libra 2000). Many investigations have been made to modify the solar tracking system to increase the efficiency of the system.

#### **1.3.1** Modeling of Photovoltaic Cell

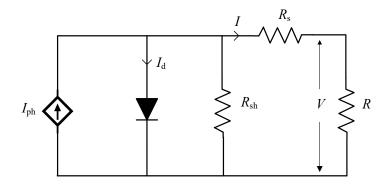

The semiconductor unit called as a photovoltaic cell is used for the electrical transformation of solar light and the phenomenon is termed as 'Photovoltaic effect'. PV cells are clustered into large units called PV modules, which are attached to form PV arrays. In order to size a solar photovoltaic array, cells are arranged in a series-parallel combination for the required energy (Ko et al. 2018). Depending on the operative conditions and field factors such as the irradiation values, sun's geometric position, and environmental temperature, the electrical power produced by a solar photovoltaic range fluctuates (Ikegami et al. 2001; De Soto et al. 2006). A solar cell is a non-linear device and can be signified as a current source model as depicted in Fig. 1.6. The equivalent circuit of PV cell includes the current source  $I_{ph}$  is the PV cell current,  $I_d$  is the diode's reverse saturation current, R is the load connected,  $R_s$  and  $R_{sh}$  are the PV cell's intrinsic series and shunt resistances.

Fig. 1.5: I-V characteristics of a typical PV module.

Fig. 1.6: Simplified equivalent circuit of a photovoltaic cell.

The typical I-V characteristics of a PV array is given by the following equation:

$$I = N_p I_{ph} - N_p I_d \left[ exp \left( \frac{qV}{kTAN_s} - 1 \right) \right]$$

where, *V* is the output voltage (V) of the PV array, *I* is the output current (A) of the PV array, *I*<sub>d</sub> is the reverse saturation current of the cell, *q* is the charge of an electron ( $q = 1.60217662 \times 10^{-19}$  C), *N*<sub>s</sub> is the number of series connected cells, *N*<sub>p</sub> is the number of parallel connected modules, *A* is the ideality factor of pn junction, *k* is the boltzmann's constant ( $k = 1.38064852 \times 10^{-23}$  joule per kelvin), *T* is the temperature of the cell.

#### **1.4 DC-DC Power Conversion**

DC-DC converters are the power electronic circuits which are used in most of the power conditioning systems to convert a dc voltage to a different dc voltage level. DC-DC converters are broadly classified as follows:

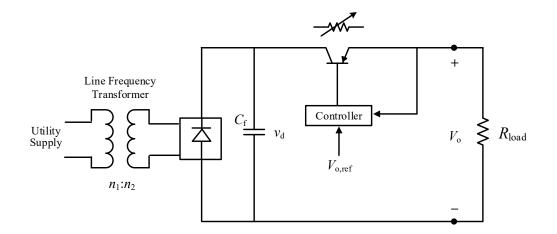

#### 1.4.1 Linear Voltage Regulator

The linear voltage regulator is used to convert the dc voltage level to a lower dc voltage level as shown in Fig.1.7. The transistor base current is adjusted accordingly to regulate the output dc voltage over a range of zero to rated output voltage  $v_d$ . The variations in line and load are compensated by adjusting base current to regulate the output voltage. The transistor is made to operate in a linear region which acts as a variable resistor to control the output, which results in low efficiency. Linear voltage regulators can handle only low power levels (typically below 20 W) and have very low power density because they require low-frequency (50 or 60 Hz) line transformers and filters which are relatively large and bulky.

Fig. 1.7: Linear voltage regulator.

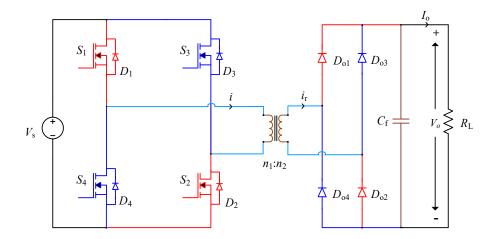

#### 1.4.2 Switched Mode Converters

In these converters, pulse width modulation (PWM) is used for the output voltage regulation. The output voltage is controlled by changing the duty ratio of the power semiconductor switches. These converters are hard switched circuits that suffer from high switching losses. It also limits the use of these converters at high-frequency switching because they result in higher switching losses and higher switching stresses. The switching losses increase with the switching frequency which results in low efficiency and difficulty in dissipating the heat from the semiconductor switches. Some of the examples of switched mode DC-DC converters are: buck converter, boost converter, cuk converter etc. Switched mode converters with isolation are flyback converter, forward converter, half bridge converter, full bridge converter (see Fig. 1.8) etc.

Fig. 1.8: Full bridge switched mode converter.

#### 1.4.3 Soft-Switching Converters

The operation of the switch mode PWM converters exhibits some drawbacks such as higher switching losses and electromagnetic interference (EMI) problems due to hard-switching. These inadequacies become more significant when a high-frequency operation is considered in an effort to increase the power density with the decrease in the size of magnetics and filters. Hence to overcome these issues, different converter topologies have been developed which offer soft-switching. The soft-switching techniques such as, zero voltage switching (ZVS) (Lin et al. 2008; Pinheiro and Barbi 1993; Safaee et al. 2015; Wu et al. 2008) and zero current switching (ZCS) (Li and Xu 2017; Mousavi and Moschopoulos 2014; Wang et al. 2005; Wang 2005) are used to reduce the switching losses which in-turn increases the efficiency of the converter. One such approach to create these soft-switching techniques is by using resonant converters. The resonant converters are based on an LC resonant tank which creates a high-frequency oscillatory current, making the semiconductor devices to switch with zero voltage or zero current, resulting in low switching losses and stresses. Soft-switching converters constrain the switching of the power semiconductor devices to time intervals when the voltage across the switch or the current through the switch is nearly zero.

#### 1.5 Switching Mechanism

#### 1.5.1 Hard-Switching

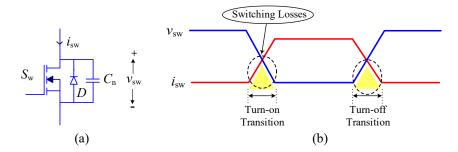

Imperfect switching is a major contributor to power loss in the converters. Switching devices absorb power when they are made to turn-on or turn-off when both voltage and current are non-zero. The simultaneous presence of the voltage across the switch and current through it during switching causes a certain amount of power to dissipate within the device. The voltage and current characteristics of hard-switching is shown in Fig. 1.9. The power device has to withstand high voltage and current simultaneously which causes high switching losses and stresses. These losses are very significant for high switching frequency converters which result in low efficiency and thus require large heat sinks. Furthermore, hard-switching creates sharp changes in voltage and current (dv/dt and di/dt), producing electromagnetic interferences (EMIs).

Fig. 1.9: (a) Typical MOSFET device with snubber. (b) Waveforms of switch voltage ( $v_{sw}$ ) and current ( $i_{sw}$ ) during hard-switching.

#### 1.5.2 Soft-Switching

Soft-switching is used to reduce the switching losses in converter. Reduced switching losses result in a smaller size of heat sinks and a notable increase in the efficiency of the converter. The switching power loss is reduced by making either current or voltage zero during the switching transitions. The voltage and current waveforms during soft-switching process are shown in Figs. 1.10-1.11. In earlier days, lossy snubbers or RCD snubbers were usually added to the power circuits so that the switching losses can be reduced to some extent. But with the high switching frequency operation, the switching losses still remain more significant reducing the efficiency of the converter. Hence, to have better efficiency, LC resonant tank circuits are included in the converter to reduce switching losses. The use of LC resonant tank creates oscillatory (usually sinusoidal) current and/or voltage waveforms so that zero voltage switching (ZVS) or zero current switching (ZCS) soft-switching features are created for the switching devices. The operation of the converter at high-frequency reduces the size of magnetics and filter but increases switching power loss; hence soft-switching techniques such as ZVS and ZCS are used to reduce switching losses, electrical stresses and EMIs which in-turn increases the efficiency of the converter. The ZVS and ZCS techniques used for soft-switching are explained in the following sections.

#### 1.5.3 Zero Voltage Switching

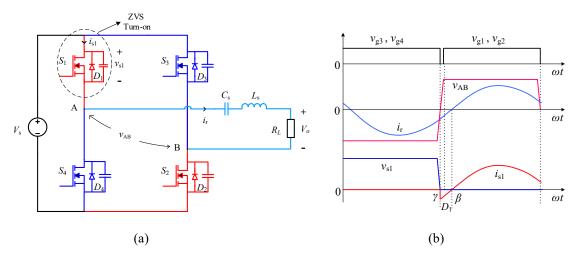

The resonant tank circuit is used for most of the converters to accomplish softswitching features. The resonant tank is a combination of inductors and capacitors which are used to create an oscillatory current. The voltage across the switch is made to zero during the turn-on instant for obtaining ZVS. To attain ZVS, the converter is to be designed to operate in lagging power factor (PF) mode (above resonance). The resonant current  $i_r$  lags the inverter output voltage  $v_{AB}$  [see Fig. 1.10(b)]. This can be achieved by selecting the operating switching frequency of the converter above the resonant frequency while designing.

The full bridge resonant converter shown in Fig. 1.10(a) is used to explain the operation of ZVS. The typical waveforms of voltage  $v_{s1}$  across the switch  $S_1$  and current  $i_{s1}$  through it are shown in Fig. 1.10(b) to describe ZVS operation. When the gating signals  $v_{gs3}$  and  $v_{gs4}$  are removed and since the resonant current  $i_r$  cannot change instantaneously, the direction of the current is maintained through antiparallel diodes  $D_1$  and  $D_2$ . It is observed in Fig. 1.10(b) that at the instant  $\omega t = \gamma$  the diode  $D_1$  becomes forward biased with the negative current  $i_r$  flowing through it. Before the instant  $\omega t = \beta$ , the switch  $S_1$  is given with a gating pulse  $v_{gs1}$ . However, the switch does not turn-on since the antiparallel diode  $D_1$  becomes zero, since the gating signal for  $S_1$  is already given, the switch  $S_1$  turns on conducting the positive current. Since the antiparallel diode of the switch  $S_1$  was conducting just before the switch conducts, ZVS turn-on of the switch is achieved. Hence, turn-on switching losses are eliminated.

Fig. 1.10: ZVS mechanism. (a) Full bridge resonant converter (b) Waveforms of voltage across and current through switch  $S_1$ .

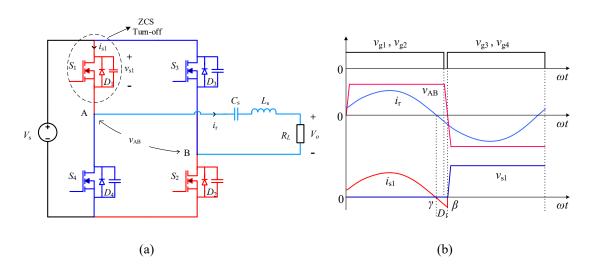

#### 1.5.4 Zero Current Switching

The full bridge series resonant converter with the resonant tank of inductance  $L_r$ and capacitance  $C_r$  is shown in Fig 1.11(a). The sinusoidal current is created using the resonant tank of the converter and ZCS of the inverter switches can be achieved. If the current through the switch is zero at the instant of switch turn-off (i.e., removal of gating signal) then it is said to be ZCS. To attain ZCS, the converter is to be designed to operate in leading PF mode (below resonance). The resonant current  $i_r$  leads the inverter output voltage  $v_{AB}$  [see Fig. 1.11(b)]. This can be achieved by selecting the operating switching frequency of the converter to be below the resonant frequency. The typical waveforms of voltage  $v_{s1}$  across the switch  $S_1$  and current  $i_{s1}$  through it are shown in Fig. 1.11(b) to describe ZCS operation. At the instant  $\omega t = \gamma$ , current  $i_{s1}$  goes to zero and later tend towards negative forward biasing the antiparallel diode  $D_1$ . The diode  $D_1$  conducts with the negative current from the instant  $\gamma$  to  $\beta$  as shown in Fig. 1.11(b) and  $S_1$  is made to turn-off by removing a gating pulse  $v_{gs1}$  at this instant( $\omega t = \beta > \gamma$ ) to achieve ZCS. Hence, turn-off switching losses are eliminated.

Fig. 1.11: ZCS mechanism. (a) Full bridge resonant converter (b) Waveforms of voltage across and current through switch  $S_1$ .

## **1.6 Motivation for the Work**

A power conditioning unit is required to convert the fluctuating power from the renewable energy sources into a constant power. Resonant converters are the most attractive DC-DC converters used in power conditioning unit as they provide low switching losses, stresses and EMIs, resulting in high efficiency. High-frequency operation of the resonant converters results in reduced size and weight of the converter which is advantageous in most of the renewable energy applications. Maintaining softswitching over the entire operating range of input voltage and load variations in fuel cell based power generation is a challenge due to wide variations in the fuel cell stack voltage which depends on the rate of fuel flow. In today's rapidly growing semiconductor technology, the work done till now on power converters appears limited and requires further work to be done. This necessity has been the motivation for this dissertation to take up the research on high-frequency full bridge resonant converter for applications with wide variation in input voltage and loading conditions.

In the literature, there are number of converter topologies described for the utility interfacing. However, there is limited systematic performance evaluation of the chosen front-end converter topology with the different gating control schemes for the applications involving wide variations in input voltage and loading conditions. This missing part motivated for this dissertation. The full bridge CLL resonant converter gives good performance (Asa et al. 2015; Chakraborty et al. 1999; Tschirhart and Jain 2008) and the investigations done on full bridge CLL resonant DC-DC converters is limited. The CLL resonant converter topology incorporates the advantageous features of both SRC and PRC resulting in; (i) good light load efficiency (ii) better voltage regulation. Hence, high-frequency transformer isolated full bridge CLL resonant DC-DC converter with capacitive output filter applied with regular phase-shift and modified PWM gating scheme is proposed and investigations are performed in Chapter 3 of this dissertation. The detailed modeling and the steady-state analysis of the converter is

carried out. The soft-switching of the converter is achieved for wide variations in loading conditions.

Maintaining soft-switching over the entire operating range of variation in input voltage and load is a major challenge for the present application. The converter loses soft-switching feature at higher input voltages. This missing part motivated for the further research and the selected converter has been configured with zero-voltage-transition (ZVT) auxiliary circuit as proposed in Chapter 4 of this dissertation. The proposed converter topology is able to provide soft-switching for an entire range of variations in input voltage and loading conditions. This converter topology can be used for medium power applications.

In the single-phase bridge converters, the power handling capability is limited and if any of the switches of the converter fails, the power transfer is stopped. This missing step motivated for further research. The three-phase interleaved CLL resonant converter with fixed frequency modified PWM gating control is proposed in Chapter 5 of this dissertation. The three identical full bridges along with CLL resonant tank on the primary side of high-frequency (HF) transformer are connected in parallel as interleaved structure.

In generating the power from renewable energy sources, the output voltage is highly fluctuating. The DC-DC converters as a significant part of the power electronic interface play an important role in conditioning power to provide constant output voltage. Compact and high efficient converters maintaining soft-switching for variations in input voltage and load are the necessities required for these renewable energy applications. The research work is directed towards the high-frequency CLL resonant DC-DC power converter operated with fixed frequency control. The proposed converter topologies can be effectively used for the renewable energy applications.

On the basis of motivations discussed, the objectives of the dissertation are set and discussed in the following Section.

## 1.7 Objectives

Based on the motivations for the work on the chosen research topic, the following objectives are set:

1. To propose a fixed frequency phase-shift and modified PWM gating scheme applied to a high-frequency transformer isolated CLL-type resonant DC-DC power converter for wide variations in input voltage and load and to perform the following.

a) Mathematical modeling b) Steady state analysis c) Design and, d) Simulations

- 2. To build the experimental prototype of the converter indicated in objective #1 and verify the performance with theoretical predictions.

- 3. To propose a zero-voltage-transition (ZVT) circuit to the resonant converter indicated in objective#1 and analyse the performance.

- To build an experimental prototype of the converter indicated in objective #1 with ZVT circuit and verify the performance with theoretical predictions made in objective #3.

- 5. To propose an interleaved operation of the converter indicated in objective#1 and analyse the performance through simulations.

The research work is done to accomplish the set objectives and the outcomes are presented in the dissertation. The outline of the dissertation is stated in the next Section.

## **1.8** Outline of the Dissertation

The research outcome of the set objectives is presented in three chapters [3, 4, and 5] of the dissertation. The description of the layout of the dissertation is as follows:

Chapter 2 describes the literature review on soft-switching resonant converters for renewable energy applications. Various resonant converter topologies are studied and their advantages and disadvantages are defined. The need for ZVT auxiliary circuit in the resonant converter to turn-on the switches with zero voltage switching is discussed. The gating control scheme to regulate the output voltage of the resonant converters is described. The selection of the resonant converter topology and gating control scheme is explained in detail. The proposed resonant converter should be able to operate with soft-switching for wide variations in input voltage and loading conditions.

In chapter 3, a high-frequency CLL resonant DC-DC converter operated with phase-shift and modified PWM gating scheme is described. Different modes of operation of the converter with both the gating schemes are described and studied in detail. Detailed modeling and the steady-state analysis of the converter is performed by using fundamental harmonic approximation approach. PSIM simulation is carried out and the experimental prototype is built to substantiate theoretical performance predictions. The simulation and experimental outcomes are presented and compared. The converter provides ZVS to all the switches at minimum input voltage for wide variations in load. At maximum input voltage, the converter when applied with phase-shift gating scheme loses ZVS for two switches whereas the converter when applied with modified PWM gating scheme loses only one switch resulting in better efficiency. Hence, modified PWM gating scheme is more advantageous than normal phase-shift gating scheme for the converter with application of variations in input voltage and loading conditions.

In chapter 4, high-frequency isolated full bridge ZVT CLL resonant DC-DC converter is presented. The CLL resonant converter fed with normal phase-shift gating scheme requires two ZVT auxiliary circuits to assist all the main switches to turn-on with ZVS. The usage of two auxiliary circuits in the converter causes conduction losses and also increases the cost and complexity of the converter. Whereas, the ZVT CLL resonant converter proposed in this chapter, fed with modified PWM gating scheme requires only one ZVT auxiliary circuit to provide ZVS for all the main switches. The ZVT auxiliary circuit helps the switch losing ZVS to turn-on with ZVS which reduces the switching losses in-turn enhances the efficiency of the converter. Various operating modes of the converter with ZVT auxiliary circuit are described in detail with the help of typical operating waveforms and equivalent circuit diagrams. The procedure for

optimum design and typical design curves are described. The PSIM simulation results for various operating conditions are presented. The theoretical and simulation results are validated with the help of an experiment and the results are presented.

Chapter 5 describes the three-phase interleaved CLL resonant converter applied with a fixed frequency modified PWM gating scheme. The interleaved operation of the proposed converter is explained with the key waveforms and detailed modeling and analysis are carried out. The choice of optimum parameters of the converter design is described. The PSIM simulations is carried out to substantiate theoretical predictions of the converter for various operating conditions. The interleaving technique has several advantages such as, the converter can deal with high power level, low output ripple current, reduced stress on the switches, high conversion efficiency and partial load can be supplied in case of a fault in any of the phases of the converter.

Chapter 6 gives a summary of the research contributions of the dissertation with the conclusions and suggestions for future work.

## **Chapter 2**

# LITERATURE REVIEW ON SOFT-SWITCHING RESONANT CONVERTERS

For medium (<10 kW) and high-power (10 kW – 100 kW) applications, highfrequency full bridge resonant converters can be widely used to have a compact and efficient converter for power conditioning (Agamy et al. 2016, 2015; Dincan et al. 2019). Introduction to various resonant converter topologies and different gating control schemes is presented in this Chapter.

The organization of this chapter is as follows: Introduction of resonant converters and description of various topologies is given in Section 2.1. The different gating control schemes used to regulate the output voltage of the converter are explained in Section 2.2. The selection of converter topology and gating control scheme for the study is described in Section 2.3. Conclusion is given in Section 2.4.

## 2.1 Resonant Converters

Increasing demand for saving energy and requirement of reduction in the size of power converters have increased significant research and efforts in developing high power density and high efficiency resonant converters (Bhat 1992; Cho et al. 1994; Chuang et al. 2011b; Ivensky et al. 1999a; Jang and Jovanović 2004; Kazimierczuk and Wang 1992; Oruganti and How 1993; Rajagopalan et al. 1990; Redl et al. 1994; Steigerwald 1988; Wang 2006). The resonant converter topologies are formed by using different combinations of inductors and capacitors. Proper designing of the converter that can make the current through inductor and capacitor to oscillate/resonate will help in attaining soft-switching of the converter switches. Soft-switching process comprises

of zero-voltage switching (ZVS) and/or zero-current switching (ZCS) techniques. These soft-switching techniques avoids simultaneous occurrence of voltage and current thereby the switching losses are eliminated. Hence, use of resonant converters with high-frequency switching operation leads to the following advantages:

- High efficiency

- Reduced size of magnetics and filters

- Low EMIs

- Reduced stresses on the switches

- High power density

The isolated high-frequency (HF) resonant converters are an essential component of power conditioning unit in grid interfacing. The basic structure of the resonant converter includes HF switched inverter, resonant tank, HF transformer, diode rectifier and filter as shown in Fig. 1.2. These converters are used to regulate the output power for variations in input voltage and loading conditions. Various switching strategies are applied to resonant converters to vary the duty ratio for controlling the output voltage along with soft-switching features. The resonant converter topologies are broadly classified in the following Sections:

#### 2.1.1 Series Resonant Converters

The series resonant converter (SRC) (Daneshmand et al. 2017; Daryaei et al. 2019; Ivensky et al. 1999b; Kazimierczuk and Wang 1992; Lu et al. 2008; Sabate and Lee 1991; Safaee et al. 2016; Steigerwald 1988; Wu et al. 2017a) has its resonant tank which is composed of capacitor  $C_s$  and inductor  $L_s$  connected in series as shown in Fig. 2.1. The advantage of the series resonant converter is that the currents in the power devices decrease as the load decreases. This allows the device conduction losses to decrease as the load decreases, thus maintaining high light-load efficiency. Another advantage of this converter is that the series resonant capacitor  $C_s$  on the primary side will act as a dc blocking capacitor.

Fig. 2.1: Series resonant converter.

The series-resonant converter has the disadvantage that the output voltage cannot be regulated for the no-load case. The output dc filter capacitor of the converter must carry high ripple current. This is a significant disadvantage for applications with low output voltage and high current (Steigerwald 1988). For this reason, series resonant converter with capacitive filter is considered suitable for high-output-voltage low-output-current applications.

#### 2.1.2 Parallel Resonant Converters

The parallel resonant converter (PRC) (Bonache-Samaniego et al. 2017; Ghahderijani et al. 2017; Haskew and Nelms 1994; Hsu et al. 2017; Johnson and Erickson 1988; Kim et al. 2018; Oruganti and How 1993) includes resonant tank comprising of series connected inductor  $L_s$  and parallel connected capacitor  $C_p$  as shown in Fig. 2.2. The parallel resonant converter is able to control the output voltage at no-load by varying the switching frequency. The parallel resonant converter is suitable for low-output-voltage high-output-current applications. This is due to the fact that the dc filter on the low-voltage-output side is an inductor that limits the ripple current and therefore output capacitors capable of carrying very high ripple currents are not required.

As the load decreases, the switching frequency increases to regulate the output voltage. But the peak current in the resonant tank circuit in PRC remains relatively constant. As a result of this, the conduction losses in switches and in reactive components remain constant even during reduced load. Hence, PRC suffers from poor light-load efficiency.

Fig. 2.2: Parallel resonant converter.

## 2.1.3 Three Element Resonant Converters

The three-element topologies like LCC, LCL, CLL are reported in literature (Asa et al. 2015a; Bhat 1993, 1997a; Borage et al. 2009; Chen et al. 2015; Doradla 1995; Hu et al. 2014a; Selvaperumal and Rajan 2012; Severns 1992; Tan and Ruan 2016). Three element resonant converter topologies effectively use the parasitic components of transformer and switches which increases the performance of the converter. The converters are designed to operate for wide variations in input voltage and loading conditions while providing soft-switching features.

#### 2.1.3.1 Series-Parallel Resonant Converters (LCC Resonant Converter)

The series-parallel resonant converter (Belaguli and Bhat 2000; Bhat 1993; Chen et al. 2006; Chia and Sng 2009; Chuang et al. 2011a; Ivensky et al. 1999a; Morrison 1992; Sosa et al. 2009) shown in Fig. 2.3 utilizes the best characteristics of the series and parallel resonant converter while eliminating their disadvantages of lightload regulation and load independent current in resonant tank respectively. The peak switch current should reduce with the load, decreasing the conduction losses in the switches to keep the light-load efficiency of the LCC resonant converter high. Hence, it is advantageous to choose the converter components such that the full-load value of  $Q [Q = \omega_s L_s/R_L]$  is around 4 or 5. For these values of Q, the converter seems basically as a series resonant converter where the peak current in the resonant circuit will decrease as the load reduces. Further decrease in load will make the LCC resonant converter to resemble the characteristics of parallel resonant converter and henceforth the current in the resonant circuit and switching devices no longer decreases with load. As the LCC resonant converter involves the parallel capacitor, the converter adopts characteristics of parallel resonant conditions.

Fig. 2.3: Series-parallel resonant converter.

#### 2.1.3.2 Modified-Series Resonant Converter (LCL-Type Resonant Converter)

The modified-series or LCL-Type resonant converter is shown in Fig. 2.4. In an effort to resolve the issue of voltage regulation of series resonant converter, modified-series (LCL-Type) resonant converters were reported (Beiranvand et al. 2012; Bhat 1995b, 1997a; Doradla 1995; Du and Bhat 2015; Yang et al. 2016). In this topology of the resonant converter, series connected capacitor ( $C_s$ ) and inductor ( $L_s$ ) are inter-connected with the parallel inductor ( $L_p$ ), forming the resonant network as shown in Fig. 2.4. The leakage and magnetizing inductances of high-frequency transformer are profitably used in this converter. As part of the parallel inductor, the magnetizing inductance of the high-frequency transformer may be used and leakage inductance of high-frequency is considered as a part of the series inductor. To regulate the output voltage of the converter, only a slight variation in switching frequency is required as compared to the series resonant converter for wide variations in load.

Fig. 2.4: LCL resonant converter.

## 2.1.3.3 CLL Resonant Converter